先週部品選定してて確認していたのでここに書きます.

概要

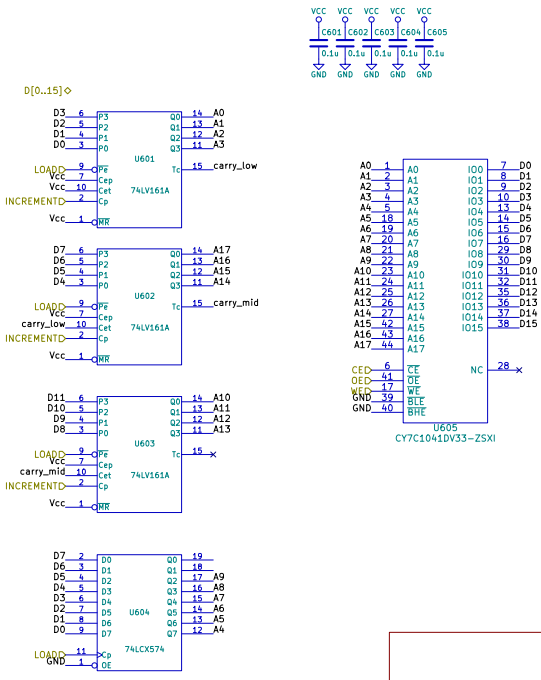

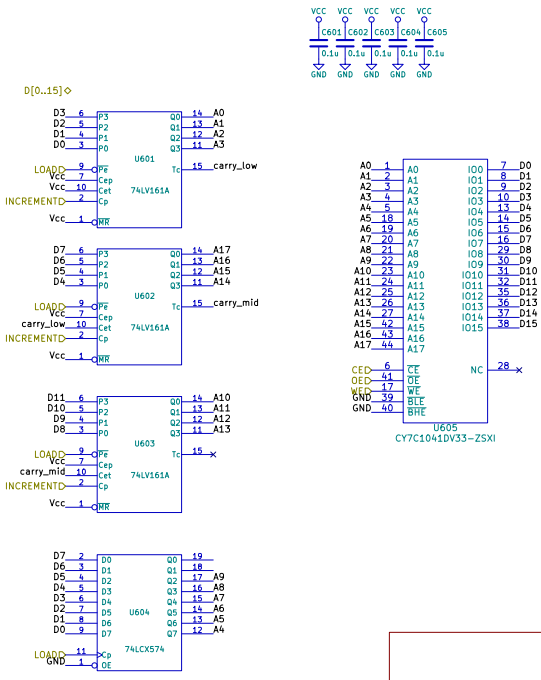

- frame buffer は 0x40000 word, 16bit databus の高速 SRAM を使用する

- 本回路はピン数削減のため, databus 16bit と制御線5本で構成される

- 制御線のうち2本で汎用ロジックICを制御し,databus 16bit から frame buffer の address bus を生成する

address bus 生成

- address bus は下位12bitを 74161 x3, 残りを 74574 で制御する

- 74161 は load で 12bit を任意に設定可かつ, counter を利用しシーケンシャルアクセスが可能

- 74574 の CLK と 74161 の LOAD を同じ線にしているので全部のaddressを load する場合は 74161 -> 74574 の順番に行なう

- address bus の配線は SRAM のピン配置に無関係で配線しやすい線に接続する

data bus 制御

- bytemask pin は GND 固定にして 16bit access 専用

- increment による address 更新から data が出てくる時間は 74LV161A の伝搬遅延と CY7C1041DV33 の read cycle の max 加算で 13.6 + 10.0 -> 23.6 ns

反省点

- 74574 ではなく 74821 にすると 74161 を1つ減らせて基板の必要な表面積を減らせる. 74821 には LCX があるが定番ではないのでやや高い.

- 設計当時は SRAM は frame buffer としてのみの利用を想定していたため, instruction RAM 兼用とした場合の都合に配慮できなかった.

- 74161 は現在の新規設計としては定番の汎用ロジックでないため、最速がシリーズが LV...A で停まっている. カウンタである都合や LCX などに比べると伝搬遅延が多い.

- 定番で早いシリーズが用意されているのは NOT, NAND, AND, OR, XOR の単純なゲートやバスバッファ(244,541)やバストランシーバ(245)とDラッチ(374,574)などに絞られる

- カウンタ(161)やシフトレジスタ(164)などはそんなに早くないのでピン数を減らしてもスピードや表面積のトレードオフになる

- 利用頻度が高い address の更新は 74161 を利用することになるので、 read / write cycle は 23.6 ns より早くすることはできない.

- つまり 74574 は 74LV161A の伝搬遅延より遅くない 74VHC574 でも構わない.